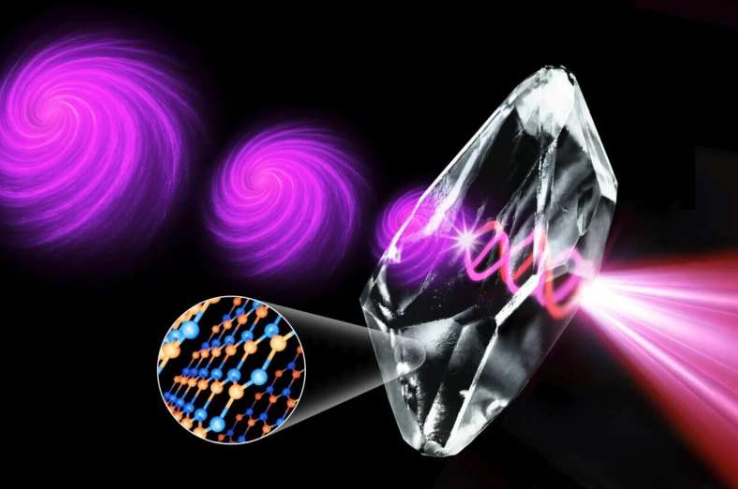

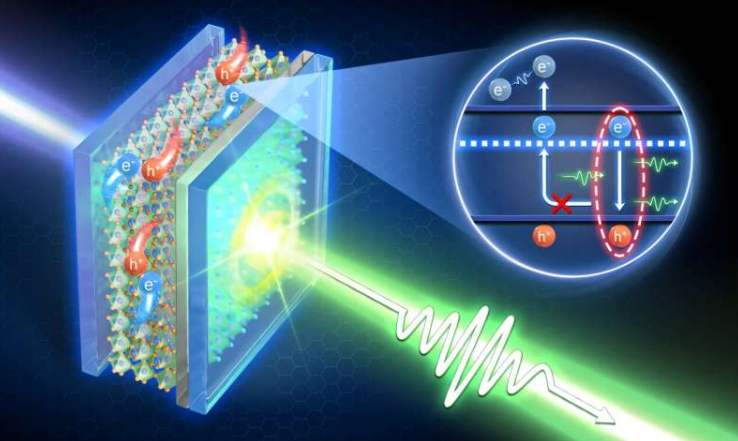

El equipo de investigación de la Universidad de California recientemente publicó resultados en la revista Journal of Lightwave Technology, logrando con éxito la integración monolítica de un láser de puntos cuánticos de arseniuro de indio en un chip fotónico de silicio, proporcionando un nuevo esquema para la aplicación a gran escala de circuitos integrados fotónicos (PIC). Esta tecnología, mediante la optimización del crecimiento de materiales y el diseño de acoplamiento óptico, reduce significativamente la pérdida de potencia óptica entre el láser y la guía de ondas de silicio, mejorando la eficiencia de integración.

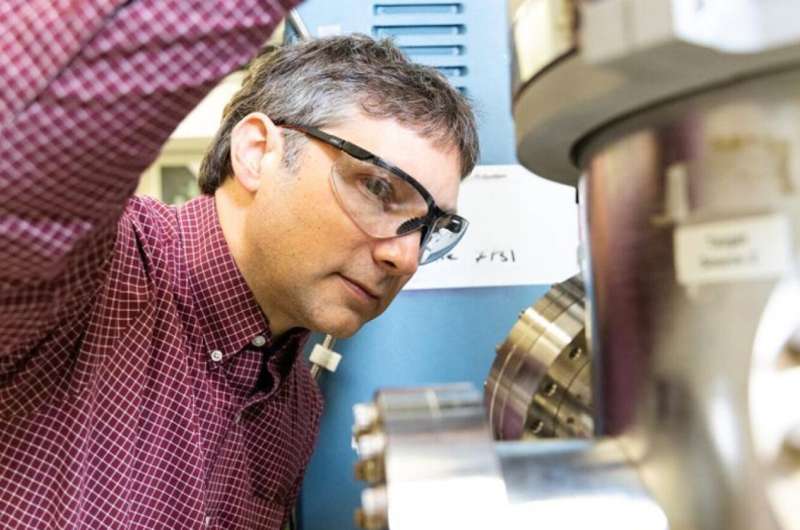

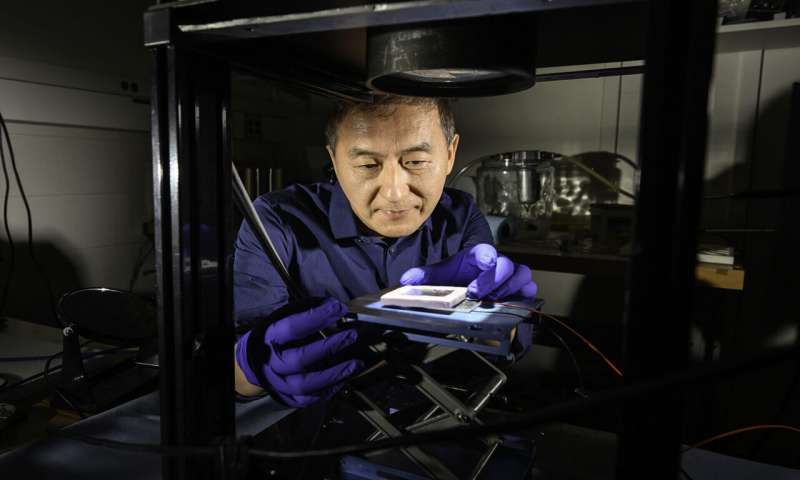

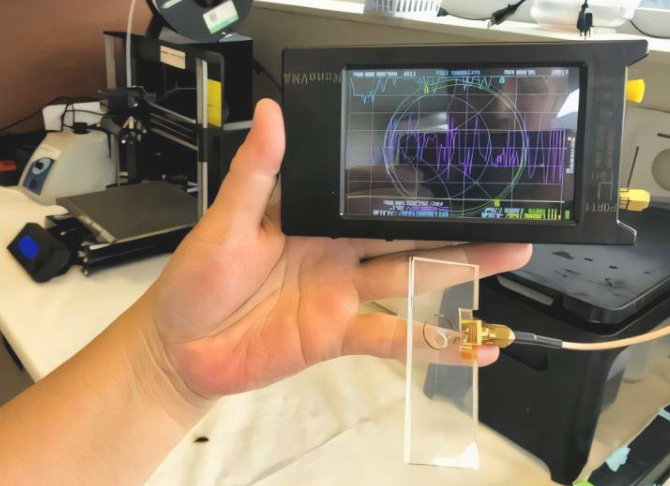

La responsable de la investigación, la doctora Rosalyn Koscica, indicó: "Los circuitos integrados fotónicos requieren fuentes de luz en chip más compactas para lograr una integración de alta densidad." El equipo adoptó un esquema de crecimiento de materiales en dos pasos, combinado con tecnología de relleno de brechas poliméricas, para preparar directamente el láser de puntos cuánticos en el sustrato de silicio. Las pruebas muestran que el dispositivo integrado opera de manera estable en la banda O, con bajas pérdidas de acoplamiento, y una vida útil de hasta 6,2 años a 35°C. Este progreso proporciona viabilidad para la fabricación a gran escala de chips fotónicos de silicio.

La ventaja de la tecnología de integración láser en chips fotónicos de silicio radica en su compatibilidad con los procesos de fabricación de semiconductores existentes y su adaptabilidad a diversos diseños de dispositivos fotónicos. La doctora Koscica señaló: "Esta tecnología puede aplicarse a diferentes circuitos integrados fotónicos sin ajustes complejos." En el futuro, mediante una mayor optimización de la estructura de los componentes fotónicos de silicio, este esquema podría promover la popularización de fuentes de luz en chip de alto rendimiento y bajo costo.